SOLUTION

FPGA動的再配置(FPGA版プラグイン機能)

FPGA動的再配置(FPGA版プラグイン機能)

1/3《概要・開発概要》 2/3《検討・実装方法》 3/3《実装と動作確認・付録》

FPGA動的再配置(FPGA版プラグイン機能)《概要・開発概要》

1. ドキュメント概要

以降、第二章の開発概要で、目的、計画などについて述べ、第三章のFPGA動的再配置の検討で、最近のFPGA動的部分再構成の動向と本件の動的再配置の違いについて述べる。第四章でSVI-06でのFPGA動的再配置の実装方法について述べ、第五章で実際のサンプルを実装し、動作確認したことについて述べて、本レポートを結ぶ。

2. 開発概要

2.1. 目的

SVI-06ではFPGAの空きリソースを活用することで、SVI-06の基本機能に加えて、ユーザ固有のロジックをユーザIPとして組み込めるようにする。ユーザIPが組み込まれたFPGAダウンロード・データは、ホストPC上のアプリケーションを通してユーザから容易に、SVI-06ボードの電源をON/OFFすることなく、ダウンロードすることを可能とする。また、SVI-06FPGAへのユーザIPの組み込みに際しては、ネットビジョンおよびユーザ間でFPGAソースを公開することなく、FPGAにダウンロードするデータを作成可能にする。

上記目的を達成すれば、以下に挙げるメリットが得られるものと考える。

・FPGAソースを公開することがないので、お互いに知的財産を守ることができる。

・単一のボードで多くの機能を切り替えて使用できるため、ボードの汎用性が高まり、低コスト化が図れる。

・メモリへの画像取り込みからホストPCへの画像転送処理などは、SVI-06の基本機能として提供されるので、ユーザは大がかりで煩雑な画像転送処理から開放されて、ユーザ固有の追加機能となるユーザIPの設計、検証、評価に集中することができる。

・ターゲットとなるカメラ・モジュールの通信I/Fが高速、高機能化しており、それらの多様なI/F、処理内容に対応する必要がある場合に、ユーザIPの変更だけで基本機能部分を変えなくてすむため、短期間での設計・検証・評価が可能になる。

2.2. SVI-06でのFPGA動的再配置

・FPGA(XC6SLX25-2FGG484C)全体のリソースで、50%程度ユーザに開放できる見込みである。・DDR2-SDRAM256MByteのうち、一部の領域をフレーム・メモリとしてユーザに開放する。

・ユーザIPとのインタフェースは、汎用バスに近い簡便なものとする。

2.3. 計画

・2012年上半期:顧客別に受託開発を開始。・2012年下半期:弊社SVI-06基本ロジックをIPとして提供または販売可能にする予定。

・2013年初期:ユーザIPのみの入替ソフトを提供または販売可能にする予定。

FPGAプラグイン開発環境リクエスト(無償期間:2014年11月~2015年1月)

FPGA動的再配置(FPGA版プラグイン機能)《検討・実装方法》

3. FPGA動的再配置の検討

3.1. FPGAの動的部分再構成の動向

Xilinx社製のVirtex4以降の高機能高級FPGAにおいては、動的部分再構成に関して、デバイスと開発ソフトの両方で対応するようになり、最近になって正式に商用サポートされるようになった。現状、Spartan6などの廉価なFPGAでは、デバイスでは、サポートされているようだが、開発ソフト(最新のISE13.2)の方ではサポートされていない。しかし、Xilinx社のFPGAでは動的再構成に関して2001年ぐらいから対応しており、一部のユーザ向けの限定機能という位置づけで、開発ソフトや設計支援ツールなしに手動で、実装できるようになっていた。正式な商用サポートではなかったため、広く普及せず、一部の研究機関等で利用されてきただけであった。

3.2. 動的再配置の要点

SVI-06に実装のSpartan6のような中小規模の限られたリソースで廉価なFPGAにこそ、目的に合わせて複数の機能を効率よく実装するために、FPGAの動的部分再構成が必要と考える。しかし、現状では開発ソフトが対応せず、商用サポートされず、手動による方法も難しいために工数がかかり、エラーがあるとFPGAを破壊してしまう恐れがある。そこで発想を転換し、Spartan6の動的再構成は、近い将来、正式に商用サポートされると考え、ユーザの要求があれば、基本機能+ユーザIPのFPGAデータをホストPCのアプリケーション・ソフトの支援によりダウンロードして、FPGA全体を入れ替えることを第一段階として進める。部分再構成と全体の再構成とで、再構成して機能が有効になるまでの時間の違いと、基本機能部分をいったん止める必要があるかどうかの違いがあるが、アプリケーション・ソフトを通してユーザからみた場合、SVI-06の使用用途としては問題ないレベルと考えられる。

このように将来的な動的部分再構成を視野に入れて、ユーザの必要に応じてFPGA全体をボードの電源をON/OFFすることなしに入れ替えることで、ホストPCのアプリ・ソフトからあたかも関数を呼び出すようにFPGAに機能を追加したり、入れ替えたりすることをここではFPGAの動的再配置と呼ぶ。

FPGAの動的再配置では、基本機能とユーザIPとの切り分けが重要となる。画像処理のデータ・フローなどを考慮して、ユーザIPのブロック分け、各ブロックが基本機能に対して配置される位置などをあらかじめ決めておく必要がある。ユーザが固有のロジックをIPとして、後から容易に設計できるようなインタフェース仕様が必要であり、基本機能ブロックにはユーザIPとのインタフェース機構または回路が必要になる。さらに、将来対応予定の動的部分再構成の観点からも、ユーザIPに対するブロック分けは重要なポイントとなる。

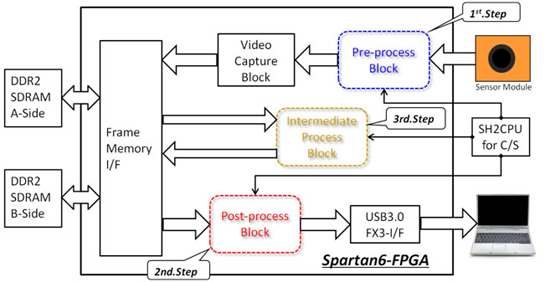

3.3. 動的再配置ブロック分けと割り当て位置

SVI-06FPGAで、ユーザIPの動的再配置に関するブロック分けと割り当て位置について検討した概略図を、以下に示す。動的再配置ブロックは、前処理(Pre-process)ブロック、中間処理(Intermediate Process)ブロック、後処理(Post-process)ブロックの3つのブロックからなるように分ける。色分けされた動的再配置ブロック以外のFPGA内のブロックは、従来のSVI-03の画像転送処理ブロックと基本的な構成は変わらず、その部分をSVI-06FPGAの基本機能ブロックとする。

3つの動的再配置するブロックの処理内容として考えられる、ユーザ固有のロジック、アプリを以下に挙げる。

●Pre-process(前処理) : カメラI/F変換、間引き、色変換、ホワイトバランスなどのカメラの付加機能など。

● Intermediate Process(中間処理):大量のメモリを必要とする処理、画像の解析、演算、フォーマット変換など。

●Post-process(後処理):色変換、フォーマット変換、UVC等ヘッダ付加、圧縮・符号化など。

センサ・モジュールからの画像は、SVI-06の動作では以下のような順序で処理され、ホストPCに転送されるものとする。

1. 動的再配置される前処理ブロックに、センサ・モジュール固有のインタフェースのまま、画像信号が入力される。前処理ブロックは、内部の基本機能ブロックに対して、標準的な画像信号インタフェース(データ/水平・垂直同期/ソース・クロック)で、画像信号を出力する。センサからの画像信号を直接受けて、画像データを参照・加工したいユーザが、この位置に前処理IPとして配置する。デフォルトの状態またはユーザによるカスタム機能が不要の場合は、前処理ブロックは従来のSVI-03と同様に動作するよう、入力から出力までスルーするブロックを配置しておく。

2. 前処理ブロックから出力された画像データは、基本機能ブロックであるVideo-Capture-Blockによって、フレーム単位に処理され、Frame Memory I/Fを通して、フレーム・メモリとして使用される DDR2SDRAMに格納される。

3. 動的再配置される中間処理ブロックでは、フレーム・メモリに格納された画像をフレーム単位で読みだして、変換処理をした後、処理後のデータをフレーム・メモリに格納する。フレーム単位で画像データを参照・加工したいユーザが、この位置に中間処理IPとして配置する。デフォルトの状態またはユーザによるカスタム機能が不要の場合は、中間処理ブロックは何も動作をしない空のブロックを配置しておく。

4. 動的再配置される後処理ブロックは、基本機能であるUSB3.0FX3-I/FブロックとFrame Memory I/Fの間の画像データをホストPCに転送する際の経路で、ストリーム的 に画像データを参照・加工したいユーザが配置する。デフォルトの状態またはユーザによるカスタム機能が不要の場合は、後処理ブロックは従来のSVI-03と同様に動作するよう、入力から出力までスルーするブロックを配置しておく。

動的再配置ブロックのコントロール、ステータスおよび制御パラメータの受け渡しは、図に示した ようにSH2CPUを介して行う。

3つの動的再配置ブロックの対応は、入出力I/Fの難易度、必要となる周辺回路の複雑さ、検討、実装にかかる工数を考慮して、図示したように以下のステップで進める。

1st.ステップ: 前処理ブロック → 2nd.ステップ: 後処理ブロック → 3rd.ステップ: 中間処理ブロック

本レポートでの実装、動作確認については、1st.ステップである前処理ブロックのみに限定する。

1. 追加機能、入れ替え機能に関する要求の検討。

2. 再配置ブロックとしての割り当て、位置決め検討。前処理、中間処理、後処理のどの位置が適切か、または複数の位置にブロックを分散して配置する必要があるかなど。

3. 公開する基本機能ブロックと動的再配置ブロック間のI/F仕様を確認、検討。

4. ユーザIPの設計、HDLソースを記述。

5. ユーザIPソースを論理合成して、ネットリストを生成。

6. 基本機能とユーザIPのネットリストを合わせて、FPGA全体のダウンロード・データ(ビットストリーム)を合成。

7. ユーザ固有のホストPCアプリ、GUIが必要な場合は、SVI-SDKAPIを呼び出してSVIsamに実装するか、SVImonのプラグインを設計、製作。

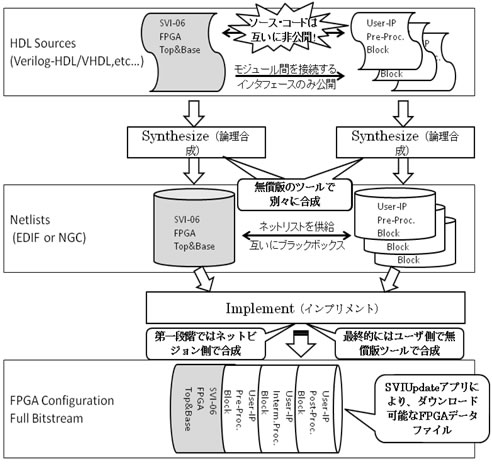

上記フローの4,5,6で、HDLによる回路記述ソースから回路を合成し、FPGA全体のビットストリームが生成されるまでの様子を以下に図示する。

1. 動的再配置される前処理ブロックに、センサ・モジュール固有のインタフェースのまま、画像信号が入力される。前処理ブロックは、内部の基本機能ブロックに対して、標準的な画像信号インタフェース(データ/水平・垂直同期/ソース・クロック)で、画像信号を出力する。センサからの画像信号を直接受けて、画像データを参照・加工したいユーザが、この位置に前処理IPとして配置する。デフォルトの状態またはユーザによるカスタム機能が不要の場合は、前処理ブロックは従来のSVI-03と同様に動作するよう、入力から出力までスルーするブロックを配置しておく。

2. 前処理ブロックから出力された画像データは、基本機能ブロックであるVideo-Capture-Blockによって、フレーム単位に処理され、Frame Memory I/Fを通して、フレーム・メモリとして使用される DDR2SDRAMに格納される。

3. 動的再配置される中間処理ブロックでは、フレーム・メモリに格納された画像をフレーム単位で読みだして、変換処理をした後、処理後のデータをフレーム・メモリに格納する。フレーム単位で画像データを参照・加工したいユーザが、この位置に中間処理IPとして配置する。デフォルトの状態またはユーザによるカスタム機能が不要の場合は、中間処理ブロックは何も動作をしない空のブロックを配置しておく。

4. 動的再配置される後処理ブロックは、基本機能であるUSB3.0FX3-I/FブロックとFrame Memory I/Fの間の画像データをホストPCに転送する際の経路で、ストリーム的 に画像データを参照・加工したいユーザが配置する。デフォルトの状態またはユーザによるカスタム機能が不要の場合は、後処理ブロックは従来のSVI-03と同様に動作するよう、入力から出力までスルーするブロックを配置しておく。

動的再配置ブロックのコントロール、ステータスおよび制御パラメータの受け渡しは、図に示した ようにSH2CPUを介して行う。

3つの動的再配置ブロックの対応は、入出力I/Fの難易度、必要となる周辺回路の複雑さ、検討、実装にかかる工数を考慮して、図示したように以下のステップで進める。

1st.ステップ: 前処理ブロック → 2nd.ステップ: 後処理ブロック → 3rd.ステップ: 中間処理ブロック

本レポートでの実装、動作確認については、1st.ステップである前処理ブロックのみに限定する。

4. 実装方法

4.1. 設計フロー

動的再配置するユーザIPに関する設計フローを以下に示す。1. 追加機能、入れ替え機能に関する要求の検討。

2. 再配置ブロックとしての割り当て、位置決め検討。前処理、中間処理、後処理のどの位置が適切か、または複数の位置にブロックを分散して配置する必要があるかなど。

3. 公開する基本機能ブロックと動的再配置ブロック間のI/F仕様を確認、検討。

4. ユーザIPの設計、HDLソースを記述。

5. ユーザIPソースを論理合成して、ネットリストを生成。

6. 基本機能とユーザIPのネットリストを合わせて、FPGA全体のダウンロード・データ(ビットストリーム)を合成。

7. ユーザ固有のホストPCアプリ、GUIが必要な場合は、SVI-SDKAPIを呼び出してSVIsamに実装するか、SVImonのプラグインを設計、製作。

上記フローの4,5,6で、HDLによる回路記述ソースから回路を合成し、FPGA全体のビットストリームが生成されるまでの様子を以下に図示する。

4.2. 動作フロー

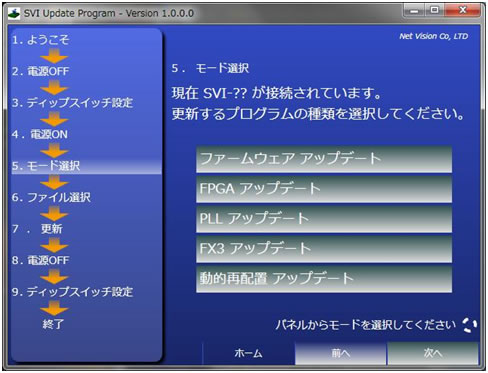

動的再配置するユーザIPを実行するまでの動作フローについて、以下に示す。1. 合成済みの動的再配置するユーザIPを含んだFPGA全体のビットストリームをホストPCの任意の場所に格納しておく。

2. SVIsam等のアプリで、SVI-06が動作中の場合は、それらのアプリをいったん終了する。

3. SVIUpdateアプリを用いて、動的再配置モードで1.のビットストリームをSVI-06FPGAにダウンロードする。

4. SVIUpdateアプリを終了し、再びSVIsamアプリを起動する。

5. 必要であればSVIsamアプリで前処理ブロックに対するコントロール・レジスタを設定する。

6. SVIsamアプリ従来と同様に画像取り込み動作を開始する。

7. 前処理ブロックが正しく動作しているか確認するか、または画像取り込み動作を見ながら、コントロール・レジスタでパラメータの調整等を行う。

以下に、SVIUpdateアプリで動的再配置モードを選択する際の実行画面を示す。

4.3. 前処理ブロックの公開インタフェース仕様

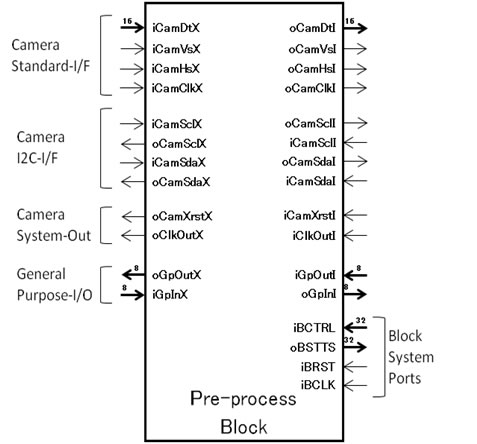

ユーザIPの設計する際に必要なインタフェースについて説明するために、ポート構成を表した前処理ブロックを以下に図示する。

左側が外部接続されるカメラ・センサに対するポートで、右側がFPGA内部側の基本機能ブロックに接続されるポートとなる。

左側のポートは、従来のSVI-03の場合の外部カメラ・センサ接続ポートと全く同様となるので、詳細な説明は省略する。

右側のFPGA内部に対しても、外部接続されるセンサ・カメラと同じポート構成を持っているので、基本機能ブロックから見れば前処理ブロックは外部接続のカメラ・センサのようにふるまう。

加えて右側には、前処理ブロックを動作させるために必要なクロックとリセット、制御に必要なコントロール/ステータスそれぞれ32bitのポートからなるBlock-System-Portsがある。

以下に、各ポートの概要を説明する表を示す。

外部接続信号と内部接続信号の名前が併記されている場合は、信号の意味、使用用途が外部と内部で同じく対応することを示す。ユーザIPを実装しないデフォルトの前処理ブロックでは、外部と内部で対応する信号が直接接続されているのと同様になる。

ユーザIPを設計する際に使用しない信号は、外部と内部で対応する信号の場合は直結しておくことで問題なく動作する。Block-System-Portsに関しては、入力は必要に応じて接続し、出力は’0’(GND)固定でよい。

iBCTRL/oBSTTSは、SH2CPUから読み書きされるコントロール・レジスタにマップされるので、前処理ブロックに対してホストPCから容易にコントロールとパラメータの送信およびステータスの受信をすることができる。

左側のポートは、従来のSVI-03の場合の外部カメラ・センサ接続ポートと全く同様となるので、詳細な説明は省略する。

右側のFPGA内部に対しても、外部接続されるセンサ・カメラと同じポート構成を持っているので、基本機能ブロックから見れば前処理ブロックは外部接続のカメラ・センサのようにふるまう。

加えて右側には、前処理ブロックを動作させるために必要なクロックとリセット、制御に必要なコントロール/ステータスそれぞれ32bitのポートからなるBlock-System-Portsがある。

以下に、各ポートの概要を説明する表を示す。

外部接続信号 |

内部接続信号 |

ビット幅 |

方向 |

概要 |

| iCamDtX | oCamDtI |

16 |

IN-OUT |

外部接続されるカメラ・センサからのデータ信号の入力 |

| iCamVsX | oCamVsI |

1 |

IN-OUT |

外部接続されるカメラ・センサからの垂直同期信号の入力 |

| iCamHsX | oCamHsI |

1 |

IN-OUT |

外部接続されるカメラ・センサからの水平同期信号の入力 |

| iCamClkX | oCamClkI |

1 |

IN-OUT |

外部接続されるカメラ・センサからのデータ・クロック信号の入力 |

| iCamSclX | oCamSclI |

1 |

IN-OUT |

外部接続されるカメラ・センサからのI2C-SCL信号の入力 |

| oCamSclX | iCamSclI |

1 |

OUT-IN |

外部接続されるカメラ・センサに対するI2C-SCL信号の出力 |

| iCamSdaX | oCamSdaI |

1 |

IN-OUT |

外部接続されるカメラ・センサからのI2C-SDA信号の入力 |

| oCamSdaX | iCamSdaI |

1 |

OUT-IN |

外部接続されるカメラ・センサに対するI2C-SDA信号の出力 |

| oCamXrstX | iCamXrstI |

1 |

OUT-IN |

外部接続されるカメラ・センサに対するリセット信号の出力 |

| oClkOutX | iClkOutI |

1 |

OUT-IN |

外部接続されるカメラ・センサに対して供給するクロック信号の出力 |

| oGpOutX | iGpOutI |

8 |

OUT-IN |

外部への汎用出力ポート |

| iGpInX | oGpInI |

8 |

IN-OUT |

外部への汎用入力ポート |

iBCTRL |

32 |

IN |

前処理ブロックを制御するためのコントロールとパラメータの入力 | |

oBSTTS |

32 |

OUT |

前処理ブロックの状態を把握するためのステータスの出力 | |

iBRST |

1 |

IN |

前処理ブロック全体を初期化するための同期リセット信号入力 | |

iBCLK |

1 |

IN |

前処理ブロック全体での動作に必要なシステム・クロック(100MHz) |

ユーザIPを設計する際に使用しない信号は、外部と内部で対応する信号の場合は直結しておくことで問題なく動作する。Block-System-Portsに関しては、入力は必要に応じて接続し、出力は’0’(GND)固定でよい。

iBCTRL/oBSTTSは、SH2CPUから読み書きされるコントロール・レジスタにマップされるので、前処理ブロックに対してホストPCから容易にコントロールとパラメータの送信およびステータスの受信をすることができる。

参考文献

関根研究室ホームページ URL:https://www.sekine-lab.naturcode.net/(公開終了)・hw/sw複合によるカラーステレオマッチングを用いた対象物追跡アプリケーション概要

・研究成果-論文項目16. Hardware Object Model and Its Application to theImage Processing

・研究成果-論文項目7. Hw/Sw混載システムに於けるHwObjectモデルとその制御手法

FPGA動的再配置(FPGA版プラグイン機能)《実装と動作確認・付録》

5. サンプルの実装と動作確認

5.1. サンプル・ユーザIPとしての前処理ブロック

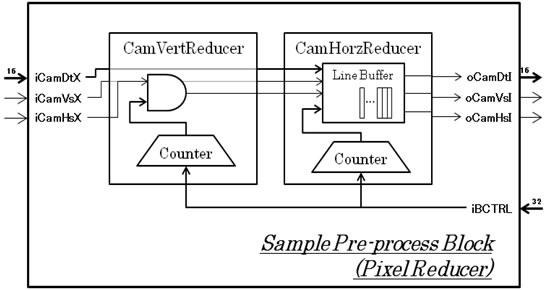

動的再配置をする前処理ブロックのサンプルとして、間引き前処理ブロックを設計、実装した。間引き前処理ブロックは、カメラから入力される画像のピクセルを間引いて縮小した画像を出力する。FPGAの基本機能ブロックからは、本来接続されているカメラより小さいサイズの画像を出力するカメラが接続されているように認識して動作をする。以下に間引き前処理ブロックの概略図を示す。

外部入力として、カメラからの標準的な画像信号(データ/垂直同期/水平同期)を取り込みながら、ピクセルを間引いて縮小した画像を内部に出力する。iBCTRLポートは、間引く量を指定するためのパラメータ入力である。CamVertReducerブロックは、カウンタの値により水平同期信号に関して1ライン全体をゲートすることで、垂直方向のラインを間引く。

CamHorzReducerブロックは、1ライン中のピクセルに関してカウンタ値により必要なデータと同期信号だけLine-Bufferに格納することで、水平方向のピクセルを間引く。内部への出力時、oCamHsIアサートで間引いたデータを間断なく出力するためにLine-Bufferが必要となる。間引き前処理ブロックのHDLソースを本レポートの付録として、末尾に掲載する。

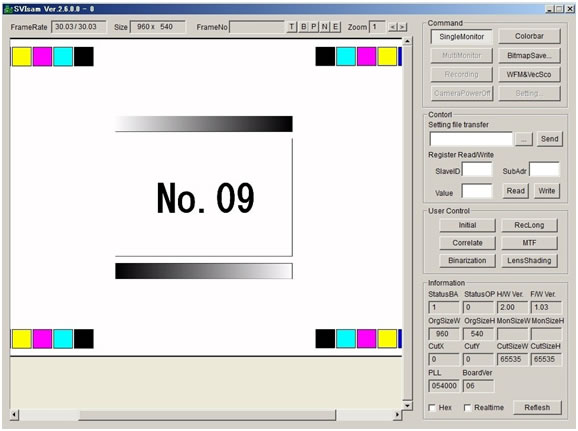

●FPGAの動的再配置により、再配置された間引きサンプル前処理ブロックに対して、ホストPCアプリのSVIsamを使用してパラメータを送信し、画像取り込み動作でホストPCに表示される取り込み画像が間引かれて縮小表示されることを確認した。

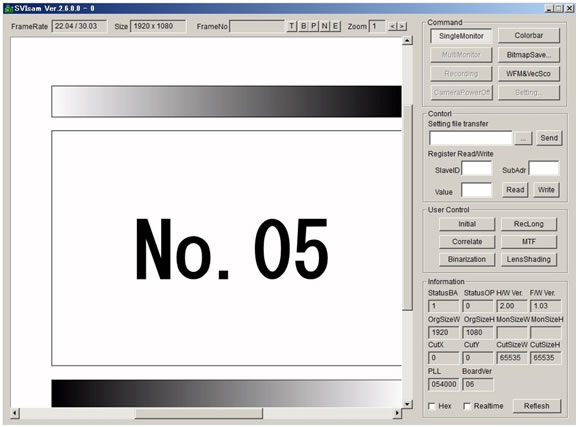

下図は、間引き前処理ブロックのユーザIPを入れない基本機能のみのFPGAで動作させた場合での、SVIsamアプリ実行画面の様子である。1080p(1920x1080プログレッシブ)の画像がそのまま取り込まれて表示されている。

CamHorzReducerブロックは、1ライン中のピクセルに関してカウンタ値により必要なデータと同期信号だけLine-Bufferに格納することで、水平方向のピクセルを間引く。内部への出力時、oCamHsIアサートで間引いたデータを間断なく出力するためにLine-Bufferが必要となる。間引き前処理ブロックのHDLソースを本レポートの付録として、末尾に掲載する。

5.2. 動作確認

●FPGAの動的再配置の第一段階として、SVI-06ボードの電源をON/OFFすることなしに、ホストPCアプリのSVIUpdateを使用して、FPGAの内容を入れ替えて、立ち上がることを確認した。●FPGAの動的再配置により、再配置された間引きサンプル前処理ブロックに対して、ホストPCアプリのSVIsamを使用してパラメータを送信し、画像取り込み動作でホストPCに表示される取り込み画像が間引かれて縮小表示されることを確認した。

下図は、間引き前処理ブロックのユーザIPを入れない基本機能のみのFPGAで動作させた場合での、SVIsamアプリ実行画面の様子である。1080p(1920x1080プログレッシブ)の画像がそのまま取り込まれて表示されている。

次の図は、前述と同じ画像入力に対して、SVIUpdateアプリによってFPGAを動的再配置し、間引き前処理ブロックのユーザIPを実装して動作させた場合での、SVIsamアプリ実行画面の様子である。1080p(1920x1080プログレッシブ)画像入力に対して、Sizeが縦横1/2に間引きされた画像(960x540)で取り込まれて表示されている。