久し振りの投稿となりました、遊んでいたわけではありません。。。

最近開発ものが多くて手をつけられませんでした。やっぱり景気良くなっているのかな。

ということで、過去の記事でSVI-06の高速版を使用して380MBpsを達成したとかありましたが、その環境に最近開発したRAW現像IPを入れて実験してみました。

結果は記事タイトルのとおり1080P、60fps、RAW10bit、FullHD画像をフレート表示することに成功いたしました~~。

フルレート表示ができるということはフルレート保存もできるわけです、ハイッ!

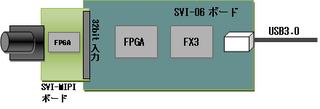

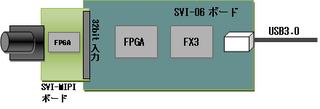

構成は左図のとおりで、1080P、60fps、RAW10bit、FullHD画像をMIPI出力するイメージセンサーを弊社SVI-MIPIボードと接続し、SVI-MIPIボード内FPGAでMIPIシリアルから32bit幅パラレルに変換し、SVI-06ボードに入力させて、SVI-06ボード内FPGAのFPGAプラグイン機能でRAW現像を行い、FX3でホストPCへ転送し表示します。

説明が長くてすみません。。。

弊社では、今までPCのソフト(SVIsam)でRAW現像を実現していましたが、これだとソフトでデモザイク処理、ゲイン補正、ガンマ補正を行っているので、画像サイズやフレームレートによっては、フルレート表示ができないことがあります。よほど高速なパソコンを用意してもVGA-30fps位がいっぱいでした。

今回SVI-06のFPGAプラグイン機構を利用して、前処理ブロック部分にRAW現像IPとしてデモザイク処理、ゲイン補正、ガンマ補正を入れました。FPGAリソースとしてロジック部分10%、ブロックRAM部分で30%程度の使用で済んでいます。

入力するRAWデータはベイヤーRGBで色の順番も4種類から選択でき、ゲイン補正、ガンマ補正では、20、30段階の係数変更を行えます。

デモザイク処理は3ライン単位で変換しますで、3ライン分のブロックRAMを使用します。

またガンマ補正用テーブルにもブロックRAMを使用しています。

このテーブルへの値の代入はソフト起動時にPCより転送してもらっています。

右図はRAW現像IP組込み前処理ブロックの構成図ともう少し詳しい説明です。

前処理ブロックの枠組みでRAW現像IPとして”RAW to RGB Development Block”(RAW現像ブロック)を組み込んでいます。

RAW現像ブロックでは、RAWベイヤー配列での1ピクセルを1クロック・サイクル毎に入力し、出力としてパラメータ指定により8bitの色深度でRGBの3色成分を含んだピクセルを1クロック・サイクル毎に出力します。

一方、高速版SVI-06では高速画像取込みに対応するため、イメージセンサーからのRAW10でのピクセル入力を32bitデータ幅に2ピクセルを割当てることで、1クロック・サイクルあたり2ピクセルでの転送レートで取込み、フレーム・メモリへ画像データを転送しています。

このため、RAW現像ブロックに入力する際に、入力クロックの2倍のクロックを生成し、2[pixel/clock]から1[pixel/clock]に変換する必要があるので、”Pixel Clock x2 and 2pxl/clk to 1pxl/clk Conversion”で変換処理をしています。

逆に、RAW現像ブロック後段での出力では、RAW10で2[pixel/clock]での転送レートと合うように、1[pixel/clock]から2[pixel/clock]へ変換し、出力クロック/データ・レートと入力クロック/データ・レートで等しいタイミングで出力されるように、”Pixel Clock /2 and 1pxl/clk to 2pxl/clk Conversion”で変換処理をして、RAW現像処理後の画像を出力しています。

上図で示すように出力直前のセレクタにより、RAW現像処理をせずにバイパスして出力することで、RAW10での入力画像データをそのまま取り込んで、ホストPCなどで評価が可能な構成となっています。

RAW現像処理後のピクセル・フォーマットとして、RGB565で出力することにより、32bitデータ幅で2[pixel/clock]での転送に適合させています。

この構成により、RAW現像処理を行った場合と行わずにバイパスさせた場合とで、画像フレームのサイズ、転送レートは常に等しくなるようにしています。

構成は左図のとおりで、1080P、60fps、RAW10bit、FullHD画像をMIPI出力するイメージセンサーを弊社SVI-MIPIボードと接続し、SVI-MIPIボード内FPGAでMIPIシリアルから32bit幅パラレルに変換し、SVI-06ボードに入力させて、SVI-06ボード内FPGAのFPGAプラグイン機能でRAW現像を行い、FX3でホストPCへ転送し表示します。

構成は左図のとおりで、1080P、60fps、RAW10bit、FullHD画像をMIPI出力するイメージセンサーを弊社SVI-MIPIボードと接続し、SVI-MIPIボード内FPGAでMIPIシリアルから32bit幅パラレルに変換し、SVI-06ボードに入力させて、SVI-06ボード内FPGAのFPGAプラグイン機能でRAW現像を行い、FX3でホストPCへ転送し表示します。